緒論

本專案用Verilog HDL語言設計了AHB總線上的SRAM控制器,SRAM存盤器在AHB總線上作為AHB slave存在,該SRAM控制器具有以下特性:

-

支持單周期的SRAM讀寫操作

-

支持低功耗作業

SRAM存盤體由兩個Bank組成,系統根據地址選中一塊/多塊Bank,未被選中的Bank將處于low-power standby模式以降低功耗 -

支持DFT功能

DFT(Design for Test,可測性設計),指通過在芯片原始設計中插入各種用于提高芯片可測驗性(包括可控制性和可觀測性)的硬體邏輯,從而使芯片變得容易測驗,大幅度節省芯片測驗的成本,

本專案中,DFT功能通過BIST(Build-in Self Test,內建自測驗)實作,采用March C-作為檢測演算法

最后,在Vivado平臺上對本專案進行了邏輯仿真與驗證

1. SRAM資料讀寫功能的實作

1.1 頂層設計架構

下面給出本專案的頂層設計架構,其中sram_top為頂層模塊,其下包含sram_interface模塊以及SRAM_core兩個子模塊

sram_interface模塊:本質是AHB總線上的slave介面,起到連接總線與SRAM存盤體的作用,具體來說:

- 將HCLK,HRESETn,HTRANS,HBURST,HWRITE,HWDATA這些來自于AHB總線的信號轉化為存盤器介面信號

- 接收存盤器8位讀資料SRAM_q,并根據總線給出的地址,整理成為32位HRDATA,然后回傳給AHB總線

sram_core模塊:包含兩塊32位SRAM存盤體Bank,其中每塊Bank包含4個8k×8的單埠SRAM,本專案中通過例化Vivado中的IP核生成,實際芯片生產應用中常通過Memory Compiler生成

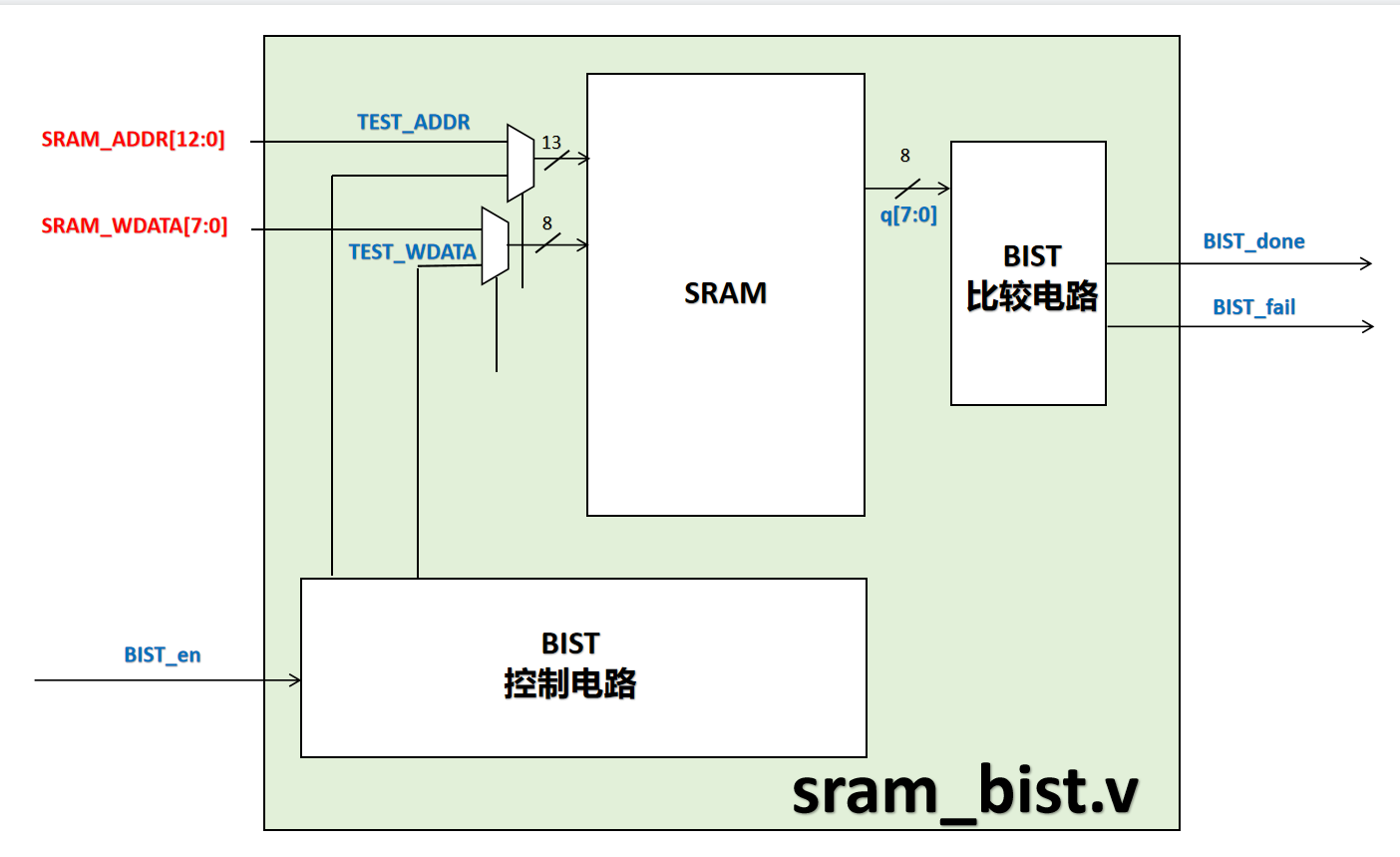

sram_bist模塊:使用SRAM讀寫功能時,可看做8k×8的單埠SRAM;當BIST功能被使能時,將會由sram_bist內部的內建自測驗電路生成Pattern對SRAM進行DFT測驗,在本專案中,BIST功能將基于March C-演算法設計,具體將在本文的第二章中介紹,在第一章中,我們將每個sram_bist模塊視為8k×8的單埠SRAM即可

在上圖中標注出了模塊的主要信號,其中紅色、藍色的信號分別代表了兩個不同的資料通路

紅色資料通路:正常使用SRAM讀寫功能時的信號,interface接收來自于AHB總線的信號,并將其轉化為SRAM所需要的控制信號和寫資料,然后再由interface將SRAM的讀資料整理后回傳AHB總線

藍色資料通路:使用DFT功能時的信號,BIST_en = 1時,DFT功能被使能,此時紅色信號全部被屏蔽,該功能用于芯片生產完畢之后,對每塊芯片進行DFT測驗以檢測是否有生產故障,該資料通路對于SRAM的邏輯功能來說,屬于冗余的部分,但是在實際芯片生產中卻是必不可少的

在本章中,我們關注紅色資料通路的電路設計,而DFT功能設計將在第二章中進行介紹

1.2 AHB SRAM讀寫時序

AHB總線時序:

其中來自AHB總線的control信號包括HTRANS,HBURST,HWRITE

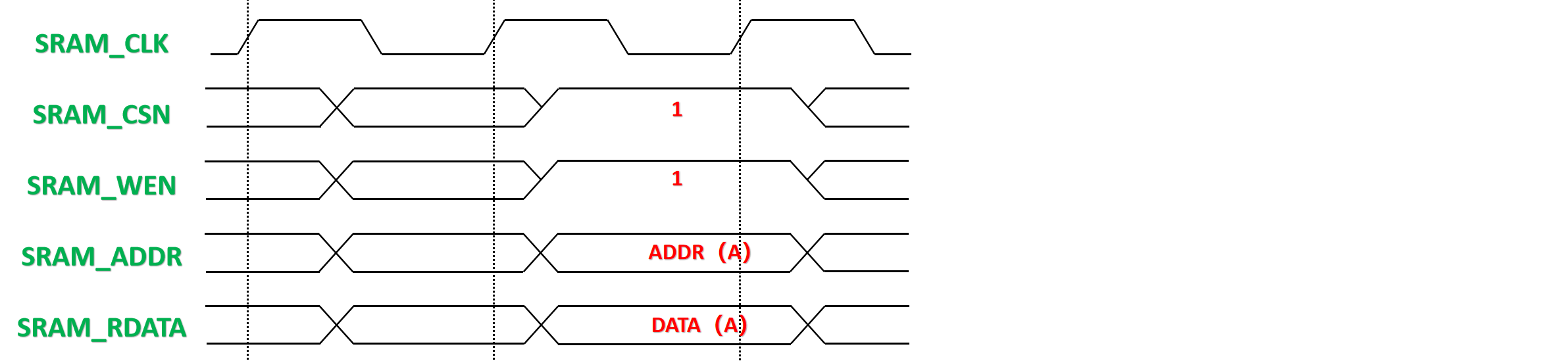

SRAM介面時序:

寫時序:

讀時序:

讀時序與寫時序的區別主要在于SRAM_ADDR的處理上:

對于寫操作,為了將地址與資料對齊,sram_interface模塊會將總線上的地址與控制信號寫入暫存器,

而對于讀操作,為了實作總線上的單周期讀出,會直接將地址送到SRAM埠(注意:SRAM的時鐘為AHB總線時鐘信號HCLK),這樣,在資料周期剛開始時,讀資料就可以回傳HRDATA,

這樣的設計具有一些局限性:由于SRAM埠上的讀地址相比于寫地址要滯后一個周期,因此當寫操作的下一個周期切換為讀操作時,會產生地址沖突,

于是,SRAM控制器會將HREADY拉低一個周期,進行緩沖,下一個周期才會重新拉高HREADY并且回傳相應的讀資料,

在連續執行多個讀操作/連續執行多個寫操作時,則不會有這樣的問題,可以以AHB總線所允許的最高的速度進行SRAM讀寫訪問,

由于在實際應用中,存盤器訪問一般不會頻繁地在讀與寫之間切換,因此這樣設計對于訪問速度帶來的代價并不大,

而這樣設計的好處,則在于可以避免為SRAM引入額外的時鐘源

1.3 RTL設計

在明確了AHB SRAM讀寫的設計需求和讀寫時序后,我們來看看具體的硬體電路是怎樣用Verilog實作的:

sram_top

首先是頂層模塊,主要內容是對兩個子模塊進行了例化,其中涉及到的信號均已經在架構圖中標明,這里不再贅述

module sram_top (

// AHB Signal

input HCLK,

input HRESETn,

input HSEL ,

input [1:0] HTRANS,

input [2:0] HBURST,

input [2:0] HSIZE ,

input HWRITE,

input [15:0] HADDR ,

input [31:0] HWDATA,

output HREADY,

output [1:0] HRESP ,

output [31:0] HRDATA,

// DFT Signal

input BIST_en ,

output BIST_done ,

output BIST_fail

);

// Wires Between SRAM_interface and SRAM_core

wire SRAM_WEN_BANK0;

wire SRAM_WEN_BANK1;

wire [12:0] SRAM_ADDR ;

wire [3:0] SRAM_CSN_BANK0;

wire [3:0] SRAM_CSN_BANK1;

wire [31:0] SRAM_WDATA ;

wire [7:0] SRAM0_q;

wire [7:0] SRAM1_q;

wire [7:0] SRAM2_q;

wire [7:0] SRAM3_q;

wire [7:0] SRAM4_q;

wire [7:0] SRAM5_q;

wire [7:0] SRAM6_q;

wire [7:0] SRAM7_q;

/*————————————————————————————————————————————————————————————————————————*\

/ SRAM Interface Instantiation \

\*————————————————————————————————————————————————————————————————————————*/

sram_interface u_interface(

//---------------AHB SIGNAL--------------

//in

.iHCLK (HCLK ),

.iHRESETn(HRESETn),

.iHSEL (HSEL ),

.iHBURST (HBURST ),

.iHWRITE (HWRITE ),

.iHTRANS (HTRANS ),

.iHWDATA (HWDATA ),

.iHADDR (HADDR ),

//out

.oHRESP (HRESP ),

.oHREADY (HREADY ),

.oHRDATA (HRDATA ),

//--------------SRAM SIGNAL--------------

//in

.iSRAM0_q(SRAM0_q),

.iSRAM1_q(SRAM1_q),

.iSRAM2_q(SRAM2_q),

.iSRAM3_q(SRAM3_q),

.iSRAM4_q(SRAM4_q),

.iSRAM5_q(SRAM5_q),

.iSRAM6_q(SRAM6_q),

.iSRAM7_q(SRAM7_q),

//out

.oSRAM_WEN_BANK0(SRAM_WEN_BANK0),

.oSRAM_WEN_BANK1(SRAM_WEN_BANK1),

.oSRAM_CSN_BANK0(SRAM_CSN_BANK0),

.oSRAM_CSN_BANK1(SRAM_CSN_BANK1),

.oSRAM_ADDR (SRAM_ADDR),

.oSRAM_WDATA (SRAM_WDATA)

);

/*————————————————————————————————————————————————————————————————————————*\

/ SRAM Core Instantiation \

\*————————————————————————————————————————————————————————————————————————*/

sram_core u_core(

//----------- From AHB ------------

.iHCLK (HCLK ),

.iHRESETn (HRESETn),

//--------- From Interface ---------

.iSRAM_WEN_BANK0 (SRAM_WEN_BANK0),

.iSRAM_WEN_BANK1(SRAM_WEN_BANK1),

.iSRAM_ADDR (SRAM_ADDR ),

.iSRAM_CSN_BANK0(SRAM_CSN_BANK0),

.iSRAM_CSN_BANK1(SRAM_CSN_BANK1),

.iSRAM_WDATA (SRAM_WDATA ),

//---------- To Interface ---------

.oSRAM0_q (SRAM0_q),

.oSRAM1_q (SRAM1_q),

.oSRAM2_q (SRAM2_q),

.oSRAM3_q (SRAM3_q),

.oSRAM4_q (SRAM4_q),

.oSRAM5_q (SRAM5_q),

.oSRAM6_q (SRAM6_q),

.oSRAM7_q (SRAM7_q),

//-------------- DFT --------------

.iBIST_en (BIST_en ),

.oBIST_done (BIST_done),

.oBIST_fail (BIST_fail)

);

endmodule

sram_interface

其次是sram_interface模塊,該模塊是本專案中重點模塊之一,負責寄存AHB總線控制信號、AHB總線地址信號,

然后根據AHB信號對SRAM存盤體進行讀寫訪問,

那么SRAM的介面信號是如何生成的呢?

CLK:直接采用AHB總線時鐘HCLK作為存盤器時鐘

CSN:片選,當地址對應BANK0時,sram0、sram1、sram2、sram3被選中,而sram3~sram7則對應BANK1

具體來說,當總線地址HADDR的值在0x0000—0x7FFF之間時地址指向BANK0,而在0x8000—0xFFFF之間時地址指向BANK1

WEN:寫使能,當HWRITE = 1時,總線對SRAM發起write操作,WEN將被拉高;

當HWRITE = 0時,總線對SRAM發起read操作,WEN將被拉低,以保證讀地址的資料不會被改寫

ADDR:地址,根據AHB SRAM讀寫時序中所介紹,

當執行SRAM寫操作時,interface模塊會將存盤器地址通過暫存器打一拍,然后在下一個周期和寫資料一起送到相應的存盤器埠上

而執行SRAM讀操作時,我們為了實作單周期讀寫,會直接將地址送到存盤器埠,這樣,就可以在下個時鐘上升沿順利地拿到存盤器回傳的讀資料,并送回AHB總線

WDATA:SRAM寫資料,來自于總線上的HWDATA[31:0],sram_interface將32位的HWDATA按照下圖順序分配給8位SRAM,作為SRAM的寫資料SRAM_WDATA

q:SRAM讀資料,每個被選中的sram_bist將回傳一個8位資料,sram_interface會將每個Bank中的4個單Byte讀資料,組合為一個完整的32位讀資料,回傳到總線上的HRDATA

HWDATA與SRAM_WDATA的對應關系,

HRDATA與SRAM_q的對應關系,

如下圖所示(以Bank0為例):

sram_interface模塊的RTL代碼如下:

module sram_interface (

//---------------AHB SIGNAL--------------

//in

input iHCLK ,

input iHRESETn,

input iHSEL ,

input iHWRITE ,

input [2:0] iHBURST ,

input [1:0] iHTRANS ,

input [31:0] iHWDATA ,

input [15:0] iHADDR ,

//out

output [1:0] oHRESP ,

output oHREADY ,

output [31:0] oHRDATA ,

//--------------SRAM SIGNAL--------------

//in

input [7:0] iSRAM0_q,

input [7:0] iSRAM1_q,

input [7:0] iSRAM2_q,

input [7:0] iSRAM3_q,

input [7:0] iSRAM4_q,

input [7:0] iSRAM5_q,

input [7:0] iSRAM6_q,

input [7:0] iSRAM7_q,

//out

output oSRAM_WEN_BANK0,

output oSRAM_WEN_BANK1,

output [3:0] oSRAM_CSN_BANK0,

output [3:0] oSRAM_CSN_BANK1,

output [12:0] oSRAM_ADDR,

output [31:0] oSRAM_WDATA

);

/*————————————————————————————————————————————————————————————————————————*\

/ Register for AHB Signal \

\*————————————————————————————————————————————————————————————————————————*/

reg iHSEL_r ;

reg iHWRITE_r ;

reg iHWRITE_2r;

reg [2:0] iHBURST_r ;

reg [1:0] iHTRANS_r ;

reg [31:0] iHWDATA_r ;

reg [15:0] iHADDR_r ;

reg [15:0] iHADDR_2r ;

always@( posedge iHCLK) begin

if(!iHRESETn) begin

iHSEL_r <= 1'b0;

iHWRITE_r <= 1'b0;

iHWRITE_2r <= 1'b0;

iHBURST_r <= 3'b0;

iHTRANS_r <= 2'b0;

iHWDATA_r <= 32'b0;

iHADDR_r <= 16'b0;

iHADDR_2r <= 16'b0;

end

else begin

iHSEL_r <= iHSEL;

iHWRITE_r <= iHWRITE;

iHWRITE_2r <= iHWRITE_r;

iHBURST_r <= iHBURST;

iHTRANS_r <= iHTRANS;

iHWDATA_r <= iHWDATA;

iHADDR_r <= iHADDR;

iHADDR_2r <= iHADDR_r;

end

end

/*————————————————————————————————————————————————————————————————————————*\

/ AHB BUS → Interface → SRAM Core \

\*————————————————————————————————————————————————————————————————————————*/

// SRAM Write Enable

assign oSRAM_WEN_BANK0 = ( iHWRITE_r == 1'b1 && iHADDR_r[15] == 1'b0) ? 1'b1 : 1'b0;

assign oSRAM_WEN_BANK1 = ( iHWRITE_r == 1'b1 && iHADDR_r[15] == 1'b1) ? 1'b1 : 1'b0;

// SRAM Bank CSN select for read ↓ select for write ↓

assign oSRAM_CSN_BANK0 = ( iHADDR_r[15] == 1'b0 || (iHADDR[15] == 1'b0 && iHWRITE == 1'b0) ) ? 4'b1111 : 4'b0000;

assign oSRAM_CSN_BANK1 = ( iHADDR_r[15] == 1'b1 || (iHADDR[15] == 1'b1 && iHWRITE == 1'b0) ) ? 4'b1111 : 4'b0000;

// SRAM Addr

wire [12:0] SRAM_WRITE_ADDR;

wire [12:0] SRAM_READ_ADDR;

assign SRAM_WRITE_ADDR = iHADDR_r[14:2]; // WRITE:addr have to wait a T , sent together with data to SRAM_CORE

assign SRAM_READ_ADDR = iHADDR [14:2]; // READ :addr send to MEM at once

assign oSRAM_ADDR = (iHWRITE_r == 1'b1) ? SRAM_WRITE_ADDR : SRAM_READ_ADDR;

// SRAM Write Data

assign oSRAM_WDATA = https://www.cnblogs.com/sjtu-zsj-990702/p/iHWDATA;

/*————————————————————————————————————————————————————————————————————————*/

/ AHB BUS ← Interface ← SRAM Core /

/*————————————————————————————————————————————————————————————————————————*/

// response to AHB MASTER

assign oHREADY = (iHSEL_r == 1'b1 && (iHWRITE_r == 1'b1 || iHWRITE_2r == 1'b0)) ? 1'b1 : 1'b0 ;

assign oHRESP = (iHSEL_r == 1'b1) ? 2'b00 : 2'b00; //OKAY = 2'b00

// sram read data

assign oHRDATA = https://www.cnblogs.com/sjtu-zsj-990702/p/(iHSEL_r == 1'b1 && iHWRITE_r == 1'b0 && iHADDR_r[15] == 1'b0) ? {iSRAM3_q, iSRAM2_q, iSRAM1_q, iSRAM0_q}:

(iHSEL_r == 1'b1 && iHWRITE_r == 1'b0 && iHADDR_r[15] == 1'b1) ? {iSRAM7_q, iSRAM6_q, iSRAM5_q, iSRAM4_q}:

32'bz;

endmodule

sram_core

接下來是頂層模塊下的sram_core,主要內容是將sram_bist模塊進行了8次例化,

因此,sram_core實際上是將這8個SRAM拼成了一個16k×32的SRAM,

sram_core的地址共15位,地址范圍為0x0000-0xFFFFF,

其中,Bank0對應0x0000-0x7FFFF;Bank1對應0x8000~0xFFFFF,

而每個sram_bist埠上的地址為sram_core上的地址右移兩位得到,共13位,地址范圍為0x0000~0x1FFF,

除此之外,sram_core將每個8k×8 SRAM的內建自測驗的輸出結果BIST_done_x,BIST_fail_x(x=0~7)進行了邏輯與/或以得到整塊sram_core存盤體的DFT測驗結果,

在執行SRAM資料讀寫功能的時候,sram_bist可以看做8k×8的單埠SRAM,

sram_core模塊的RTL代碼如下:

module sram_core (

// From AHB

input iHCLK ,

input iHRESETn,

// From sram_interface

input iSRAM_WEN_BANK0,

input iSRAM_WEN_BANK1,

input [12:0] iSRAM_ADDR ,

input [3:0] iSRAM_CSN_BANK0,

input [3:0] iSRAM_CSN_BANK1,

input [31:0] iSRAM_WDATA ,

// To sram_interface

output [7:0] oSRAM0_q,

output [7:0] oSRAM1_q,

output [7:0] oSRAM2_q,

output [7:0] oSRAM3_q,

output [7:0] oSRAM4_q,

output [7:0] oSRAM5_q,

output [7:0] oSRAM6_q,

output [7:0] oSRAM7_q,

// BIST Signals

input iBIST_en,

output oBIST_done,

output oBIST_fail

);

/*————————————————————————————————————————————————————————————————————————*\

/ BIST Ouput Logic \

\*————————————————————————————————————————————————————————————————————————*/

wire BIST_done_0;

assign oBIST_done = BIST_done_0 && BIST_done_1 && BIST_done_2 && BIST_done_3

&& BIST_done_4 && BIST_done_5 && BIST_done_6 && BIST_done_7; // done if every sram_bist dones

assign oBIST_fail = BIST_done_0 || BIST_done_1 || BIST_done_2 || BIST_done_3

|| BIST_done_4 || BIST_done_5 || BIST_done_6 || BIST_done_7; // fail if any sram_bist fails

/*————————————————————————————————————————————————————————————————————————*\

/ BANK 0 Instantiation \

\*————————————————————————————————————————————————————————————————————————*/

sram_bist u_bank0_sram0 (

// Function Mode IO

.iSRAM_CLK (iHCLK ),

.iSRAM_CSN (iSRAM_CSN_BANK0[0]),

.iSRAM_WEN (iSRAM_WEN_BANK0 ),

.iSRAM_ADDR (iSRAM_ADDR ), //13 bits SRAM ADDR

.iSRAM_WDATA(iSRAM_WDATA[7:0] ),

.oSRAM_RDATA(oSRAM0_q ),

// Test Mode IO

.iBIST_en (iBIST_en ),

.oBIST_done (BIST_done_0 ),

.oBIST_fail (BIST_fail_0 )

);

sram_bist u_bank0_sram1 (

// Function Mode IO

.iSRAM_CLK (iHCLK ),

.iSRAM_CSN (iSRAM_CSN_BANK0[1]),

.iSRAM_WEN (iSRAM_WEN_BANK0 ),

.iSRAM_ADDR (iSRAM_ADDR ), //13 bits SRAM ADDR

.iSRAM_WDATA(iSRAM_WDATA[15:8] ),

.oSRAM_RDATA(oSRAM1_q ),

// Test Mode IO

.iBIST_en (iBIST_en ),

.oBIST_done (BIST_done_1 ),

.oBIST_fail (BIST_fail_1 )

);

sram_bist u_bank0_sram2 (

// Function Mode IO

.iSRAM_CLK (iHCLK ),

.iSRAM_CSN (iSRAM_CSN_BANK0[2]),

.iSRAM_WEN (iSRAM_WEN_BANK0 ),

.iSRAM_ADDR (iSRAM_ADDR ), //13 bits SRAM ADDR

.iSRAM_WDATA(iSRAM_WDATA[23:16]),

.oSRAM_RDATA(oSRAM2_q ),

// Test Mode IO

.iBIST_en (iBIST_en ),

.oBIST_done (BIST_done_2 ),

.oBIST_fail (BIST_fail_2 )

);

sram_bist u_bank0_sram3 (

// Function Mode IO

.iSRAM_CLK (iHCLK ),

.iSRAM_CSN (iSRAM_CSN_BANK0[3]),

.iSRAM_WEN (iSRAM_WEN_BANK0 ),

.iSRAM_ADDR (iSRAM_ADDR ), //13 bits SRAM ADDR

.iSRAM_WDATA(iSRAM_WDATA[31:24]),

.oSRAM_RDATA(oSRAM3_q ),

// Test Mode IO

.iBIST_en (iBIST_en ),

.oBIST_done (BIST_done_3 ),

.oBIST_fail (BIST_fail_3 )

);

/*————————————————————————————————————————————————————————————————————————*\

/ BANK 1 Instantiation \

\*————————————————————————————————————————————————————————————————————————*/

sram_bist u_bank1_sram4 (

// Function Mode IO

.iSRAM_CLK (iHCLK ),

.iSRAM_CSN (iSRAM_CSN_BANK1[0]),

.iSRAM_WEN (iSRAM_WEN_BANK1 ),

.iSRAM_ADDR (iSRAM_ADDR ), //13 bits SRAM ADDR

.iSRAM_WDATA(iSRAM_WDATA[7:0] ),

.oSRAM_RDATA(oSRAM4_q ),

// Test Mode IO

.iBIST_en (iBIST_en ),

.oBIST_done (BIST_done_4 ),

.oBIST_fail (BIST_fail_4 )

);

sram_bist u_bank1_sram5 (

// Function Mode IO

.iSRAM_CLK (iHCLK ),

.iSRAM_CSN (iSRAM_CSN_BANK1[1]),

.iSRAM_WEN (iSRAM_WEN_BANK1 ),

.iSRAM_ADDR (iSRAM_ADDR ), //13 bits SRAM ADDR

.iSRAM_WDATA(iSRAM_WDATA[15:8] ),

.oSRAM_RDATA(oSRAM5_q ),

// Test Mode IO

.iBIST_en (iBIST_en ),

.oBIST_done (BIST_done_5 ),

.oBIST_fail (BIST_fail_5 )

);

sram_bist u_bank1_sram6 (

// Function Mode IO

.iSRAM_CLK (iHCLK ),

.iSRAM_CSN (iSRAM_CSN_BANK1[2]),

.iSRAM_WEN (iSRAM_WEN_BANK1 ),

.iSRAM_ADDR (iSRAM_ADDR ), //13 bits SRAM ADDR

.iSRAM_WDATA(iSRAM_WDATA[23:16]),

.oSRAM_RDATA(oSRAM6_q ),

// Test Mode IO

.iBIST_en (iBIST_en ),

.oBIST_done (BIST_done_6 ),

.oBIST_fail (BIST_fail_6 )

);

sram_bist u_bank1_sram7 (

// Function Mode IO

.iSRAM_CLK (iHCLK ),

.iSRAM_CSN (iSRAM_CSN_BANK1[3]),

.iSRAM_WEN (iSRAM_WEN_BANK1 ),

.iSRAM_ADDR (iSRAM_ADDR ), //13 bits SRAM ADDR

.iSRAM_WDATA(iSRAM_WDATA[31:24]),

.oSRAM_RDATA(oSRAM7_q ),

// Test Mode IO

.iBIST_en (iBIST_en ),

.oBIST_done (BIST_done_7 ),

.oBIST_fail (BIST_fail_7 )

);

endmodule

1.4 SRAM讀寫仿真驗證

在完成RTL設計后,我們撰寫了Testbench,

并在Vivado平臺上進行了簡單的讀寫仿真驗證,波形如下:

分析一下Testbench具體對SRAM發起了什么操作:

首先,T1-T7進行了六次寫操作,將6個資料依次寫入SRAM的0x0000,0x0001,0x0002,0x8000,0x8001,0x8002六個地址當中

其中前三個地址對應Bank0,后三個地址對應Bank1,

因此在T2-T4期間 SRAM_CSN_BANK0 和 SRAM_WEN_BANK0 被拉高,

在T5-T7期間 SRAM_CSN_BANK1 和 SRAM_WEN_BANK1 被拉高,

從上圖中可以看出,T7除了是Data 6的寫資料周期,也是Data 1 讀地址周期,

但是由于SRAM埠上,該周期需要執行寫Data 6的操作,

于是發生了地址沖突,無法在該周期同時進行讀Data 1

因此,在T8并沒有回傳Data 1的讀資料,HREADY被拉低,

隨后,在T9-T14,總線上HRDATA依次拿到了六個SRAM讀資料,讀出的data與T1-T7寫入的data完全一致,證明了以上SRAM控制器的設計邏輯是正確的

2. 基于March C-演算法的DFT功能

2.1 BIST架構

在設計中,SRAM讀寫模式和DFT模式的選擇通過2選1選擇器實作,當DFT模式的使能信號BIST_en = 1時,來自于sram_interface的所有信號邏輯將被忽略,

SRAM埠上的輸入信號將全部來自于sram_bist內部的BIST控制電路生成的Pattern,

對于March C-演算法,BIST控制電路會對SRAM每個地址進行“寫 → 讀 → 比較”的操作,

若所有的讀資料結果與寫入的資料是一致的,BIST_done最終將被拉高,說明該電路生產程序中沒有出現生產故障,

反之,如果比較發現有錯誤,BIST_fail最終將被拉高,該塊芯片將被報廢,

在模塊內加入DFT測驗電路,雖然會增加系統的數字面積,但同時也極大地降低了產品在測驗環節所花費的開銷成本

2.2 SRAM常見故障

首先,介紹一些常見的存盤器(比如SRAM)故障模型:

固定型故障(Stuck-At Faults,SAF):

存盤單元中的值固定為0/1(簡記為SA0/SA1),無法發生改變,固定型故障可以通過對待測單元寫入0再讀出0,然后寫入1再讀出1來進行檢測,

跳變故障(Transition Faults,TF):

存盤單元中的值無法從0跳變到1(簡記為TF(0→1)),或者從1跳變到0(簡記為TF(1→0)),需要通過寫入1到0的跳變再讀出0,然后寫入0到1的跳變再讀出1來進行檢測

耦合故障(Coupling Faults,CF):

一個存盤單元的值發生改變,導致另一個存盤單元的值發生改變,可以通過先升序對所有存盤單元進行寫讀操作,然后再降序對所有存盤單元進行寫讀操作的方法進行故障檢測

2.3 March C-演算法

March C演算法是目前應用最為廣泛的MBIST(Memory Built-In-Self-Test,存盤器內建自測驗)演算法,

March C演算法對上文提到的SAF故障,TF故障,CF故障的故障覆寫率均達到100%,

March C演算法的具體檢測流程如下:

-

從最低地址開始,在整個存盤器中依次寫入0(升序)

-

讀出最低地址,結果應為0,然后把1寫入該存盤單元,完成后地址+1,再次執行該操作,直至對整個存盤器執行該操作(升序)

-

讀出最高地址,結果應為1,然后把0寫入該存盤單元,再次讀該單元,結果應為0,完成后地址-1,再次執行該操作,直至對整個存盤器執行該操作(降序)

-

讀出最高地址,結果應為0,然后把1寫入該存盤單元,完成后地址-1,再次執行該操作,直至對整個存盤器執行該操作(降序)

-

讀出最低地址,結果應為1,然后把0寫入該存盤單元,再次讀該單元,結果應為0,完成后地址+1,再次執行該操作,直至對整個存盤器執行該操作(升序)

由于步驟4,步驟5中,加粗字體所描述的操作實際上是重復的,

因此后來有了改進的March C-演算法, 將步驟3中的加粗部分洗掉,如下:

圖中,March C-所執行的全套操作被分成了5個部分,也就是MARCH_0~MARCH_ 4

這也是本專案的BIST功能在RTL設計中,March C-狀態機所用到的5個狀態的名稱

2.4 Verilog實作March C-演算法的BIST

本專案中,內建自測驗邏輯電路位于每個sram_bist模塊中,

BIST_en作為頂層模塊的BIST使能信號,被直接接到每塊bist的BIST_en輸入使能埠,

依據March C-演算法發起的SRAM讀寫操作,是由有限狀態機控制的,該狀態機示意圖如下:

下面讓我們來看看sram_bist模塊的RTL代碼:

module sram_bist #(

//--------------- MARCH C- --------------------//

// STATE ACTION DIRECTION

// MARCH 0 write 0 ↑

// MARCH 1 read 0, write 1 ↑

// MARCH 2 read 1, write 0 ↓

// MARCH 3 read 0, write 1 ↓

// MARCH 4 read 1, write 0 ↑

//-------------------------------------------------//

// TEST_state parameters //

parameter MARCH_0 = 3'b000, // 0

parameter MARCH_1 = 3'b001, // 1

parameter MARCH_2 = 3'b010, // 2

parameter MARCH_3 = 3'b011, // 3

parameter MARCH_4 = 3'b100, // 4

parameter MARCH_finished = 3'b101, // 5

// TEST_action parameters //

parameter WRITE_0 = 2'b00,

parameter READ_0 = 2'b01,

parameter WRITE_1 = 2'b10,

parameter READ_1 = 2'b11,

// TEST_compare_result parameters //

parameter COMPARE_RIGHT = 1'b1,

parameter COMPARE_ERROR = 1'b0

)(

// Function Mode IO

input iSRAM_CLK ,

input iSRAM_CSN ,

input iSRAM_WEN ,

input [12:0] iSRAM_ADDR ,

input [7:0] iSRAM_WDATA,

output [7:0] oSRAM_RDATA,

// Test Mode IO

input iBIST_en ,

output oBIST_done ,

output oBIST_fail

);

/*————————————————————————————————————————————————————————————————————————*\

/ \

/ SRAM Normal Function Mode \

/ \

\*————————————————————————————————————————————————————————————————————————*/

// wire connected to sram's port

wire SRAM_CLK ;

wire SRAM_CSN ;

wire SRAM_WEN ;

wire [12:0] SRAM_ADDR ;

wire [7:0] SRAM_WDATA;

wire [7:0] SRAM_RDATA;

// TEST-FUN MUX

assign SRAM_ADDR = (iBIST_en == 1'b1) ? TEST_ADDR :

(iBIST_en == 1'b0) ? iSRAM_ADDR : 13'bz;

assign SRAM_CSN = (iBIST_en == 1'b1) ? 1'b1 :

(iBIST_en == 1'b0) ? iSRAM_CSN : 1'bz;

assign SRAM_WDATA = https://www.cnblogs.com/sjtu-zsj-990702/p/(iBIST_en == 1'b1) ? TEST_WDATA :

(iBIST_en == 1'b0) ? iSRAM_WDATA : 8'bz;

assign SRAM_WEN = (iBIST_en == 1'b1) ? TEST_SRAM_WEN :

(iBIST_en == 1'b0) ? iSRAM_WEN : 1'bz;

assign oSRAM_RDATA = https://www.cnblogs.com/sjtu-zsj-990702/p/SRAM_RDATA;

// IP instantiation

RAM_8K_8 u_bt_sram (

.clka (iSRAM_CLK ),// HCLK → SRAM_CLK

.ena (SRAM_CSN ),// csn → ena

.wea (SRAM_WEN ),//

.addra (SRAM_ADDR ),// unite addr

.dina (SRAM_WDATA ),// input data

.douta (SRAM_RDATA ) // output data

);

/*————————————————————————————————————————————————————————————————————————*/

/ /

/ BIST (Build-in Self Test) /

/ /

/*————————————————————————————————————————————————————————————————————————*/

// BIST CLOCK Generation

wire BIST_CLK;

assign BIST_CLK = ( iBIST_en == 1'b1) ? iSRAM_CLK : 1'b0;

// BIST RESET Generation

reg iBIST_en_r;

reg iBIST_en_2r;

wire TEST_RESET;

always @( posedge BIST_CLK) begin

if(iBIST_en && iBIST_en_r) begin

iBIST_en_r <= 1'b1;

iBIST_en_2r <= 1'b1;

end

else if ( iBIST_en ) begin

iBIST_en_r <= 1'b1;

iBIST_en_2r <= 1'b0;

end

else begin

iBIST_en_r <= 1'b0;

iBIST_en_2r <= 1'b0;

end

end

assign TEST_RESET = iBIST_en_2r ^ iBIST_en;

// BIST Controller (March C)

reg TEST_flag_finish;

reg [2:0] TEST_state;

reg [1:0] TEST_action;

reg TEST_SRAM_WEN;

reg [31:0] TEST_ADDR;

reg [7:0] TEST_WDATA;

always@( posedge BIST_CLK ) begin

if ( TEST_RESET ) begin //Synchronous Reset

TEST_flag_finish <= 1'b0;

TEST_state <= MARCH_0;

TEST_action <= WRITE_0;

TEST_SRAM_WEN <= 1'b1;

TEST_ADDR <= 13'h0000;

TEST_WDATA <= 8'b0000_0000;

end

else begin

case ( TEST_state )

//--------------- MARCH 0 ↑ -----------------//

MARCH_0 : begin

if ( TEST_ADDR == 13'h1FFF ) begin

TEST_state <= MARCH_1; //

TEST_action <= READ_0; //

TEST_SRAM_WEN <= 1'b0; // jump to MARCH_1 to read 0

TEST_ADDR <= 13'h0000; //

TEST_WDATA <= 8'bz; //

end

else if ( TEST_action == WRITE_0 ) begin

TEST_state <= TEST_state;

TEST_action <= TEST_action;

TEST_SRAM_WEN <= 1'b1;

TEST_ADDR <= TEST_ADDR + 1'b1; // addr ++

TEST_WDATA <= 8'b0000_0000; // write 0

end

end

//--------------- MARCH 1 ↑ ----------------//

MARCH_1 : begin

if ( TEST_action == WRITE_1 && TEST_ADDR == 13'h1FFF ) begin

TEST_state <= MARCH_2; //

TEST_action <= READ_1; //

TEST_SRAM_WEN <= 1'b0; // jump to MARCH_2 to read 1

TEST_ADDR <= 13'h1FFF; //

TEST_WDATA <= 8'bz; //

end

else if ( TEST_action == READ_0 ) begin

TEST_state <= TEST_state;

TEST_action <= WRITE_1; // write 1 in next clk

TEST_SRAM_WEN <= 1'b1; // write 1 in next clk

TEST_ADDR <= TEST_ADDR; // addr kept for write 1

TEST_WDATA <= 8'b1111_1111; // write 1 in next clk

end

else if ( TEST_action == WRITE_1 )begin

TEST_state <= TEST_state;

TEST_action <= READ_0; // read 0 in next clk

TEST_SRAM_WEN <= 1'b0; // read 0 in next clk

TEST_ADDR <= TEST_ADDR + 1'b1; // addr++

TEST_WDATA <= 8'bz; // read 0 in next clk

end

end

//--------------- MARCH 2 ↓ ----------------//

MARCH_2 : begin

if ( TEST_action == WRITE_0 && TEST_ADDR == 13'h0000 ) begin

TEST_state <= MARCH_3; //

TEST_action <= READ_0; //

TEST_SRAM_WEN <= 1'b0; // jump to MARCH_3 to read 0

TEST_ADDR <= 13'h1FFF; //

TEST_WDATA <= 8'bz; //

end

else if ( TEST_action == READ_1 ) begin

TEST_state <= TEST_state;

TEST_action <= WRITE_0; // write 0 in next clk

TEST_SRAM_WEN <= 1'b1; // write 0 in next clk

TEST_ADDR <= TEST_ADDR; // addr kept for write 0

TEST_WDATA <= 8'b0000_0000; // write 0 in next clk

end

else if ( TEST_action == WRITE_0 )begin //

TEST_state <= TEST_state; //

TEST_action <= READ_1; // read 1 in next clk

TEST_SRAM_WEN <= 1'b0; // read 1 in next clk

TEST_ADDR <= TEST_ADDR - 1'b1; // addr--

TEST_WDATA <= 8'bz; // read 1 in next clk

end

end

//--------------- MARCH 3 ↓ ----------------//

MARCH_3 : begin

if ( TEST_action == WRITE_1 && TEST_ADDR == 13'h0000 ) begin

TEST_state <= MARCH_4;

TEST_action <= READ_1; // jump to MARCH_4 to read 1

TEST_SRAM_WEN <= 1'b0;

TEST_ADDR <= 13'h0000;

TEST_WDATA <= 8'bz;

end

else if ( TEST_action == READ_0 ) begin

TEST_state <= TEST_state; // write 1 in next clk

TEST_action <= WRITE_1; // write 1 in next clk

TEST_SRAM_WEN <= 1'b1; // write 1 in next clk

TEST_ADDR <= TEST_ADDR; // addr kept for write 1

TEST_WDATA <= 8'b1111_1111; // write 1 in next clk

end

else if ( TEST_action == WRITE_1 )begin

TEST_state <= TEST_state; // read 0 in next clk

TEST_action <= READ_0; // read 0 in next clk

TEST_SRAM_WEN <= 1'b0; // read 0 in next clk

TEST_ADDR <= TEST_ADDR - 1'b1; // addr--

TEST_WDATA <= 8'bz; // read 0 in next clk

end

end

//--------------- MARCH 4 ↑ ----------------//

MARCH_4 : begin

if ( TEST_action == READ_0 && TEST_ADDR == 13'h1FFF ) begin

TEST_flag_finish <= 1'b1;

TEST_state <= MARCH_finished;

TEST_action <= 2'bz;

TEST_SRAM_WEN <= 1'bz;

TEST_ADDR <= 13'hz;

TEST_WDATA <= 8'bz;

end

else if ( TEST_action == READ_1 ) begin

TEST_state <= TEST_state;

TEST_action <= WRITE_0; // write 0 in next clk

TEST_SRAM_WEN <= 1'b1; // write 0 in next clk

TEST_ADDR <= TEST_ADDR; // addr kept for write 0

TEST_WDATA <= 8'b0000_0000; // write 0 in next clk

end

else if ( TEST_action == WRITE_0 )begin

TEST_state <= TEST_state;

TEST_action <= READ_0; // read 0 in next clk

TEST_SRAM_WEN <= 1'b0; // read 0 in next clk

TEST_ADDR <= TEST_ADDR; // addr kept for read 0

TEST_WDATA <= 8'bz; // read 0 in next clk

end

else if ( TEST_action == READ_0 )begin

TEST_state <= TEST_state;

TEST_action <= READ_1; // read 1 in next clk

TEST_SRAM_WEN <= 1'b0; // read 1 in next clk

TEST_ADDR <= TEST_ADDR + 1'b1; // addr++

TEST_WDATA <= 8'bz; // read 1 in next clk

end

end

MARCH_finished : begin

TEST_flag_finish <= 1'b1;

TEST_state <= TEST_state;

end

default: begin

TEST_flag_finish <= 1'b0;

TEST_state <= MARCH_0;

TEST_action <= WRITE_0;

TEST_SRAM_WEN <= 1'b1;

TEST_ADDR <= 13'h0000;

TEST_WDATA <= 8'b0000_0000;

end

endcase

end

end

// Compare SRAM_RDATA with Ideal Result

reg TEST_compare_result;

always@( posedge BIST_CLK ) begin

// Reset the Comparsion Result

if ( TEST_RESET ) begin

TEST_compare_result <= COMPARE_RIGHT; // COMPARE_RIGHT = 1'b1

end

// Read 0 in March_1

else if ( TEST_state == MARCH_1 && TEST_action == WRITE_1 ) begin

if ( SRAM_RDATA =https://www.cnblogs.com/sjtu-zsj-990702/p/= 8'b0000_0000) TEST_compare_result <= TEST_compare_result && 1'b1;

else TEST_compare_result <= TEST_compare_result && 1'b0;

end

// Read 1 in March_2

else if ( TEST_state == MARCH_2 && TEST_action == WRITE_0 ) begin

if ( SRAM_RDATA =https://www.cnblogs.com/sjtu-zsj-990702/p/= 8'b1111_1111) TEST_compare_result <= TEST_compare_result && 1'b1;

else TEST_compare_result <= TEST_compare_result && 1'b0;

end

// Read 0 in March_3

else if ( TEST_state == MARCH_3 && TEST_action == WRITE_1 ) begin

if ( SRAM_RDATA =https://www.cnblogs.com/sjtu-zsj-990702/p/= 8'b0000_0000) TEST_compare_result <= TEST_compare_result && 1'b1;

else TEST_compare_result <= TEST_compare_result && 1'b0;

end

// Read 1 in March_4

else if ( TEST_state == MARCH_4 && TEST_action == WRITE_0 ) begin

if ( SRAM_RDATA =https://www.cnblogs.com/sjtu-zsj-990702/p/= 8'b1111_1111) TEST_compare_result <= TEST_compare_result && 1'b1;

else TEST_compare_result <= TEST_compare_result && 1'b0;

end

// Read 0 in March_4

else if ( TEST_state == MARCH_4 && TEST_action == READ_1 && TEST_ADDR != 13'h0000) begin

if ( SRAM_RDATA =https://www.cnblogs.com/sjtu-zsj-990702/p/= 8'b0000_0000) TEST_compare_result <= TEST_compare_result && 1'b1;

else TEST_compare_result <= TEST_compare_result && 1'b0;

end

else begin

TEST_compare_result <= TEST_compare_result ;

end

end

assign oBIST_done = ( TEST_flag_finish && TEST_compare_result ) ? 1'b1 : 1'b0;

assign oBIST_fail = ( TEST_flag_finish && !TEST_compare_result ) ? 1'b1 : 1'b0;

endmodule

2.4 BIST的仿真驗證

最后,BIST功能同樣在Vivado平臺上進行了邏輯仿真,

整個BIST程序共BIST_en = 1開始,一共花費了約1600μs完成,

最后BIST_done被拉高,這是必然的 ,因為邏輯仿真中不涉及實際芯片制造中的各種故障,

我們先從宏觀上看仿真波形:

從波形中可以看到,MARCH_0狀態持續時間最短,這是因為MARCH_0對于每個地址操作僅為WRITE_0,

而MARCH_1,MARCH_2,MARCH_3狀態分別要進行讀和寫兩個操作,因此每個狀態下的總周期數均為MARCH_0狀態的2倍,

MARCH_4則更長,共READ_1,WRITE_0,READ_0三個操作,總周期數為MARCH_0狀態的3倍,

接下來看看MARCH_0和MARCH_1狀態之間的轉換波形:

其他幾段狀態轉化處的波形也是同理,在此不在一一標注解釋了,具體如下:

MARCH_1狀態和MARCH_2狀態之間的波形:

MARCH_2狀態和MARCH_3狀態之間的波形:

MARCH_3狀態和MARCH_4狀態之間的波形:

MARCH_4狀態最后一段波形:

完成MARCH_4后,BIST_done被拉高,代表BIST結束,

以上,就是關于AHB-SRAN的BIST模式下的邏輯仿真解讀,

最后附上兩種作業模式下的Testbench:

點擊查看代碼

`timescale 1ns / 1ps

module sram_tb #(

//HRESP

parameter OKAY = 2'b00 ,

parameter ERROR = 2'b01 ,

parameter SPLIT = 2'b10 ,

parameter RETRY = 2'b11 ,

//HTRANS

parameter IDLE = 2'b00 ,

parameter BUSY = 2'b01 ,

parameter SEQ = 2'b10 ,

parameter NONSEQ = 2'b11 ,

//HSIZE

parameter BYTE = 3'b000 ,

parameter WORD = 3'b001 ,

parameter DWORD = 3'b010 ,

//HBURST

parameter SINGLE = 3'b000 ,

parameter INCR = 3'b001 ,

parameter WRAP4 = 3'b010 ,

parameter INCR4 = 3'b011 ,

parameter WARP8 = 3'b100 ,

parameter INCR8 = 3'b101 ,

parameter WARP16 = 3'b110 ,

parameter INCR16 = 3'b111

)();

// input output declaration

reg HCLK;

reg HRESETn;

reg HSEL ;

reg [1:0] HTRANS;

reg [2:0] HBURST;

reg [2:0] HSIZE ;

reg HWRITE;

reg [15:0] HADDR ;

reg [31:0] HWDATA;

wire HREADY;

wire [1:0] HRESP ;

wire [31:0] HRDATA;

// BIST IO

reg BIST_en;

wire BIST_done;

wire BIST_fail;

// top module instantion

sram_top u_test(

.HCLK (HCLK ),

.HRESETn(HRESETn),

.HSEL (HSEL ),

.HTRANS (HTRANS ),

.HBURST (HBURST ),

.HSIZE (HSIZE ),

.HWRITE (HWRITE ),

.HADDR (HADDR ),

.HWDATA (HWDATA ),

.HREADY (HREADY ),

.HRESP (HRESP ),

.HRDATA (HRDATA ),

.BIST_en (BIST_en ),

.BIST_done(BIST_done),

.BIST_fail(BIST_fail)

);

// Excitation Vector Generation

initial begin

forever #10 HCLK = ~HCLK; //50Mhz

end

initial begin

HCLK = 0;

HRESETn = 0;

// Choose BIST Mode/ FUNC Mode to run simulation

/*————————————————————————————————————————————————————————————————————————*\

/ Testbench for BIST Mode \

\*————————————————————————————————————————————————————————————————————————*/

/*

BIST_en = 1;

end

*/

/*————————————————————————————————————————————————————————————————————————*\

/ Testbench for FUNC Mode \

\*————————————————————————————————————————————————————————————————————————*/

HRESETn = 0;

BIST_en = 0;

HSEL = 0;

HTRANS = 3'b111;

HBURST = 2'b11;

HSIZE = 3'b111;

HWRITE = 1'b0;

HADDR = 16'h0000; //HADDR[1:0] have to be 2'b00 ( 4n )

HWDATA = https://www.cnblogs.com/sjtu-zsj-990702/p/32'h0;

#65 HRESETn = 1;

//-------------------------WRITE MEM---------------

#20

// write control0

HSEL = 1;

HTRANS = NONSEQ;

HBURST = SINGLE;

HSIZE = WORD;

HWRITE = 1'b1;

HADDR = 16'h0000;

#20

// data0 → mem(0x0000)

HWDATA = https://www.cnblogs.com/sjtu-zsj-990702/p/32'h11223344;

// write control 1

HWRITE = 1'b1;

HADDR = 16'h0004;

#20

// data1 → mem(0x0004)

HWDATA = https://www.cnblogs.com/sjtu-zsj-990702/p/32'h55667788;

// write control 2

HWRITE = 1'b1;

HADDR = 16'h0008;

#20

// data2 → mem(0x0008)

HWDATA = https://www.cnblogs.com/sjtu-zsj-990702/p/32'h99AABBCC;

//// write control 3

//HWRITE = 1'b1;

//HADDR = 16'h000C;

#20

// data3 → mem(0x000C)

HWDATA = https://www.cnblogs.com/sjtu-zsj-990702/p/32'hAAAAAAAA;

// write control 4

HWRITE = 1'b1;

HADDR = 16'h0010;

#20

// data4 → mem(0x0010)

HWDATA = https://www.cnblogs.com/sjtu-zsj-990702/p/32'hBBBBBBBB;

// write control 5

HWRITE = 1'b1;

HADDR = 16'h0014;

#20

// data5 → mem(0x0014)

HWDATA = https://www.cnblogs.com/sjtu-zsj-990702/p/32'hCCCCCCCC;

// write control 6

HWRITE = 1'b1;

HADDR = 16'h8000;

#20

// data6 → mem(0x8000)

HWDATA = https://www.cnblogs.com/sjtu-zsj-990702/p/32'hDDDDDDDD;

// write control 7

HWRITE = 1'b1;

HADDR = 16'h8004;

#20

// data7 → mem(0x8004)

HWDATA = https://www.cnblogs.com/sjtu-zsj-990702/p/32'hEEEEEEEE;

// write control 8

HWRITE = 1'b1;

HADDR = 16'h8008;

#20

// data8 → mem(0x8008)

HWDATA = https://www.cnblogs.com/sjtu-zsj-990702/p/32'hFFFFFFFF;

// read control 0

HWRITE = 1'b0;

HADDR = 16'h0000;

//--------------READ MEM----------------

#20

// MASTER FINDS HREADY=0, SO MASTER WAITS

#20

// read control 1

HWRITE = 1'b0;

HADDR = 16'h0004;

HWDATA = https://www.cnblogs.com/sjtu-zsj-990702/p/32'h00000000; // to test if hwdata will work when HWRTIE = 0

#20

// read control 2

HWRITE = 1'b0;

HADDR = 16'h0008;

#20

// read control 3

HWRITE = 1'b0;

HADDR = 16'h000C;

#20

// read control 4

HWRITE = 1'b0;

HADDR = 16'h0010;

#20

// read control 5

HWRITE = 1'b0;

HADDR = 16'h0014;

#20

// read control 6

HWRITE = 1'b0;

HADDR = 16'h8000;

#20

// read control 7

HWRITE = 1'b0;

HADDR = 16'h8004;

#20

// read control 8

HWRITE = 1'b0;

HADDR = 16'h8008;

#100

$finish();

end

endmodule

至此,本專案的所有內容已介紹完畢,

轉載請註明出處,本文鏈接:https://www.uj5u.com/houduan/550406.html

標籤:Verilog

上一篇:Auto-GPT嘗鮮使用